Exentensión de la ISA de RISC-V para funciones probabilísticas

Las redes neuronales bayesianas (BNNs) nos permiten obtener métricas de incertidumbre relacionadas con los datos procesados, y la incertidumbre generada por el modelo seleccionado. Hemos identificado cómo estas métricas pueden utilizarse para varias aplicaciones prácticas, como identificar predicciones que no alcanzan el nivel de precisión requerido, o identificar cuándo las predicciones se ven afectadas por el aumento del nivel de ruido en los datos de entrada. Sin embargo, es importante tener en cuenta el mayor coste computacional asociado a las BNN, ya que su naturaleza probabilística requiere métodos de inferencia más complejos. Estas extensiones de ISA pueden reducir la necesidad de costosas aproximaciones basadas en software y permitir una utilización más eficiente de los recursos de hardware, haciendo que el aprendizaje profundo bayesiano sea más práctico para aplicaciones en tiempo real y edge computing.

BnnRV Toolchain

BnnRV es una cadena de herramientas diseñada para generar código fuente C optimizado para la inferencia de modelos BNN entrenados con BayesianTorch. Al traducir los modelos entrenados a C, BnnRV permite el despliegue de BNN conscientes de la incertidumbre en dispositivos con recursos limitados.

El paso hacia delante de una BNN requiere el muestreo de las distribuciones de pesos aprendidas durante el entrenamiento. Estas distribuciones son gaussianas y deben generarse mediante un algoritmo RNG gaussiano.

El muestreo gaussiano sigue siendo costoso desde el punto de vista computacional, incluso cuando se utiliza un algoritmo sencillo. Para resolver este problema, hemos propuesto una optimización que sustituye las distribuciones gaussianas por distribuciones uniformes para la inferencia, reduciendo significativamente la complejidad computacional del muestreo de pesos.

Esta optimización aprovecha el Teorema Central del Límite (CLT), asumiendo que las salidas de las neuronas BNN siguen una distribución gaussiana, incluso si las propias distribuciones de pesos no son gaussianas. Las neuronas BNN, al igual que las de las NN tradicionales, realizan operaciones MAC. Estas operaciones de acumulación son la base para aplicar el CLT. El código para la inferencia BNN, que incorpora la optimización de peso Uniforme, se basa en un algoritmo RNG Uniforme y dos operaciones MAC de punto fijo: la primera para la generación de peso y la segunda para la acumulación de peso estándar utilizada en las NNs. Una operación MAC de punto fijo implica un desplazamiento de bits para ajustar la escala después de la multiplicación, lo que resulta en un total de tres instrucciones por operación MAC.

Extensiones RISC-V

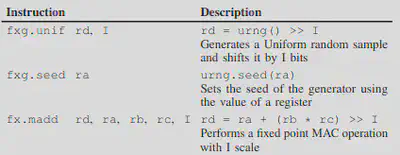

Estas extensiones de ISA pueden reducir la necesidad de costosas aproximaciones basadas en software y permitir una utilización más eficiente de los recursos de hardware, haciendo que el aprendizaje profundo bayesiano sea más práctico para aplicaciones en tiempo real y edge computing.Hemos mejorado el rendimiento de la inferencia BNN con dos nuevas instrucciones clave, una MAC de punto fijo y un RNG Uniforme. Además, se ha incluido una instrucción complementaria para la configuración de semillas aleatorias por si fuera necesario.

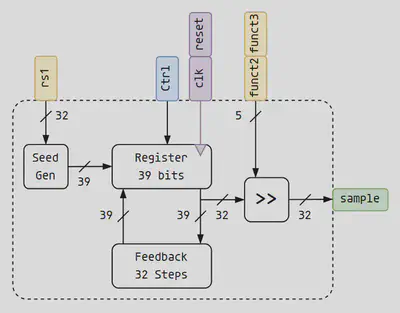

Utilizando esta extensión, el cálculo crítico de la inferencia BNN sólo requiere la ejecución de tres instrucciones de ensamblaje, lo que requerirá sólo tres ciclos en nuestro núcleo RISCV. Para implementar la unidad funcional RNG Uniforme, se utilizó un registro de desplazamiento de retroalimentación lineal (LFSR). Un LFSR consta de un registro y una red de realimentación que utiliza puertas XOR para implementar un polinomio generador, produciendo un bit aleatorio por ciclo. Sin embargo, la generación de múltiples bits con baja correlación requiere un método más complejo. Para generar muestras de 32 bits, este trabajo utiliza un LFSR de 39 bits con un mecanismo lookahead de 32 pasos y un desplazador para establecer la escala de la muestra.

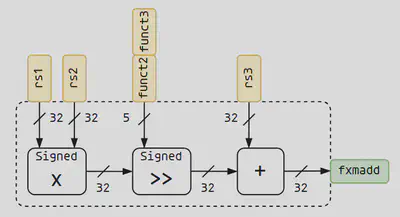

Para generar muestras de 32 bits, este trabajo utiliza un LFSR de 39 bits con un mecanismo de anticipación de 32 pasos y un desplazador para ajustar la escala de la muestra. La unidad aritmética de coma fija utiliza un hardware de multiplicación discreta de 32 bits, un sumador de 32 bits y un desplazador.

La unidad aritmética de coma fija utiliza un hardware de multiplicación discreta de 32 bits, un sumador de 32 bits y un desplazador. La escala de coma fija representa el número de bits asignados a la parte fraccionaria de un número y puede almacenarse utilizando 5 bits para una precisión de 32 bits. La instrucción fx.madd utiliza la codificación R4 RISCV. Esta codificación proporciona 5 bits de control divididos en dos campos, funct2 y funct3. El tamaño de 5 bits permite codificar el valor de escala, utilizado para definir el número de bits asignados a la parte fraccionaria de un número, dentro de esos campos como un inmediato, dentro de los 32 bits del formato de la instrucción.

El uso de valores inmediatos significa que el código necesita ser recompilado cada vez que cambian las escalas de punto fijo, lo que no debería ocurrir a menudo una vez desplegado el modelo BNN.

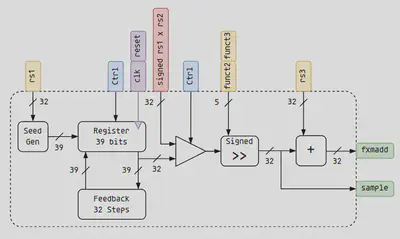

Una implementación más optimizada combina ambas unidades funcionales y comparte el hardware del shifter. Además, en lugar de utilizar un multiplicador discreto, utiliza el hardware multiplicador ya presente en el núcleo RISCV base, lo que reduce los requisitos de área.

Resultados experimentales

De media, el muestreo de una distribución Uniforme utilizando el método de software propuesto consigue un aumento de velocidad de 4,94×, mientras que utilizando las instrucciones RISCV propuestas se obtiene un aumento de velocidad de 8,93×.

La implementación optimizada da como resultado una reducción media del consumo de energía del 87,79%.