Tolerancia a Fallos Permanentes en aceleradores para CNNs

Este trabajo ha explorado la posibilidad de reducir drásticamente el voltaje de las memorias de activación en aceleradores de inferencia CNN para reducir el consumo energético. Para abordar el impacto causado en la precisión de las CNN por los fallos permanentes en las celdas de bits como consecuencia de la reducción de voltaje, se han propuesto un par de mecanismos hardware de bajo coste basados en enfoques de flipping y patching. Este trabajo es consecuencia de un estudio de caracterización que identificó el impacto en la precisión de diferentes patrones de fallo en memorias de activación.

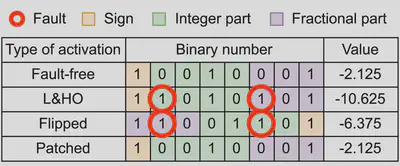

La técnica de fliping y patching se basa en la observación de que las activaciones con fallos en el byte más significativo (activaciones de Alto Orden o HO) degradan en gran medida la precisión de las CNN. Además, un pequeño número de activaciones con fallos tanto en el byte más significativo como en el menos significativo (activaciones de Bajo y Alto Orden o L&HO) también comprometen la precisión de algunas CNN. El enfoque propuesto consiste en un par de técnicas. En primer lugar, introducimos un mecanismo de inversión de palabras para tratar las activaciones HO. A continuación, proponemos un enfoque de parcheo para tratar las activaciones L&HO.

Técnica Flip

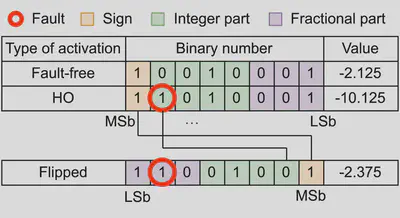

El objetivo de esta técnica es minimizar el peso de los bits defectuosos en las activaciones HO. Asumiendo una representación de datos little endian, las activaciones HO de N bit sólo contienen fallos en las posiciones de bit de N∕2 a N-1. Tras hacer flip a una activación, el bit que ocupa la posición i-ésima pasa a ocupar la posición (N-1-i)-ésima. La técnica de flip garantiza que las activaciones HO se conviertan en activaciones LO, lo que reduce significativamente el impacto de un fallo en la magnitud de la activación.

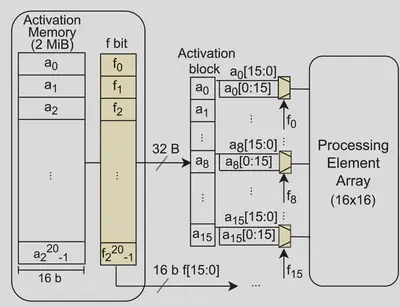

Para diferenciar entre las activaciones HO (flipped) y las restantes (non flipped), el diseño propuesto incluye un bit de control f asociado a cada activación. Este bit se establece, para diferentes niveles de Vdd, durante las pruebas posteriores a la fabricación, antes de desplegar el dispositivo para su funcionamiento real. Por lo tanto, es necesario añadir multiplexores 2:1, controlados por el bit f, para seleccionar entre una activación original, que no requiere ninguna modificación, y una activación invertida.

Técnica Patch

La técnica flip no elimina el impacto de las activaciones L&HO en la precisión de la CNN. La técnica del patch consiste en una pequeña cache, denominada patching cache, que almacena el valor original (sin fallos) de dichas activaciones.

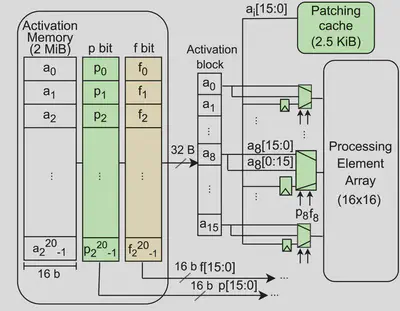

Al igual que los bits f para el enfoque de la técnica flipping, el mecanismo de patching requiere un bit de control p por activación para determinar si una activación solicitada se encuentra o no en la patching cache. Los multiplexores 2:1 se convierten en multiplexores 4:1 para seleccionar entre una activación original, la activación flipped y la patched. Las lecturas en la patching se realizan ciclo a ciclo a granularidad de palabra (activación). Por lo tanto, se necesitan latches antes de los multiplexores para almacenar temporalmente las activaciones de lectura antes de enviar el bloque a la matriz PE.

Resultados experimentales

Los resultados experimentales han demostrado que, en comparación con un acelerador CNN convencional alimentado a un voltaje seguro de 0,6 V, un acelerador mejorado alimentado a 0,54 V con Flip and Patch reduce el consumo medio de energía de las memorias de activación en un 10,5%, manteniendo la precisión original (sin fallos) con un impacto insignificante en el rendimiento del sistema (menos del 0,05%).